E/S

mediante Interrupciones

El

problema con E/S programada es que el CPU tiene que esperar un tiempo

considerable a que el módulo de E/S en cuestión esté preparado para recibir o

transmitir los datos. El CPU debe estar comprobando continuamente el estado del

módulo de E/S. Se degrada el desempeño

del sistema.

Una

alternativa es que el CPU tras enviar una orden de E/S continue realizando

algún trabajo útil. El módulo de E/S interrumpirá al CPU para solicitar su

servicio cuando esté preparado para intercambiar datos. El CPU ejecuta la

transferencia de datos y después continua con el procesamiento previo.

Se

pueden distinguir dos tipos: E/S síncrona y E/S asíncrona

- E/S Síncrona: cuando la operación de E/S finaliza, el control es retornado al proceso que la generó. La espera por E/S se lleva a cabo por medio de una instrucción wait que coloca al CPU en un estado ocioso hasta que ocurre otra interrupción. Aquellas máquinas que no tienen esta instrucción utilizan unloop. Este loop continua hasta que ocurre una insterrupción transfiriendo el control a otra parte del sistema de operación. Sólo se atiende una solicitud de E/S por vez. El sistema de operación conoce exactamente que dispositivo está interrumpiendo. Esta alternativa excluye procesamiento simultáneo de E/S.

- E/S Asíncrona: retorna al programa usuario sin esperar que la operación de E/S finalice. Se necesita una llamada al sistema que le permita al usuario esperar por la finalización de E/S (si es requerido). También es necesario llevar un control de las distintas solicitudes de E/S. Para ello el sistema de operación utiliza una tabla que contiene una entrada por cada dispositivo de E/S (Tabla de Estado de Dispositivos). La ventaja de este tipo de E/S es el incremento de la eficiencia del sistema. Mientras se lleva a cabo E/S, el CPU puede ser usado para procesar o para planificar otras E/S. Como la E/S puede ser bastante lenta comparada con la velocidad del CPU, el sistema hace un mejor uso de las facilidades.

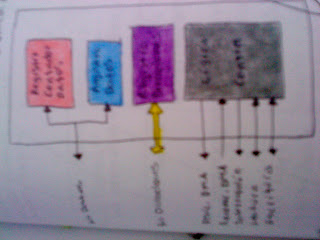

E/S

mediante DMA

(Direct Memory Access)

La

E/S con interrupciones, aunque más eficiente que la E/S programada, también

requiere la intervención del CPU para transferir datos entre la memoria y el

módulo de E/S.

Consideren

el siguiente ejemplo. Cuando se va a leer una línea desde un terminal, el

primer carácter escrito es enviado al computador. Cuando el carácter es

recibido por el controlador, éste interrumpe al CPU. El CPU le da servicio a la

interrupción y luego continua con el proceso que estaba ejecutando. Esto es

posible cuando el dispositivo es muy lento comparado con el CPU. Entre un

carácter y otro el CPU lleva a cabo gran cantidad de procesamiento. Pero qué

sucede cuando estamos trabajando con dispositivos de E/S más veloces?

Tendríamos interrupciones muy seguidas y se estaría desperdiciando mucho

tiempo.

Para

evitar esto, se utiliza DMA para dispositivos de E/S de alta velocidad. E1

controlador del dispositivo transfiere un bloque de datos desde o para susbuffers de

almacenamiento a memoria directamente sin intervención del CPU. Solo se produce

una interrupción por bloque en lugar de tener una interrupción por cada byte (o

palabra).

Por

ejemplo, un programa solicita una transferencia de datos. El Sistema de

Operación busca un buffer disponible. El controlador de DMA

tiene sus registros actualizados con las direcciones del fuente y del destino y

la longitud de la transferencia . Por lo general esta actualización es

realizada por el manejador de dispositivo (rutina). Se indica al controlador de

DMA a través de bits de control en un registro de control pare que inicie la

operación de E/S. Mientras tanto el CPU puede llevar a cabo otras operaciones.

El controlador de DMA interrumpe el CPU cuando la transferencia ha sido

terminada . El CPU interviene solo al comienzo y al final de la transferencia.

ReflexiónSe me hixo más eficiente la técnica de E/S mediante DMA, ya que con esta técnica la computadora puede sguir realizando otras operacione mientras atiende a los distintos procesos que así lo requieran.

No hay comentarios.:

Publicar un comentario